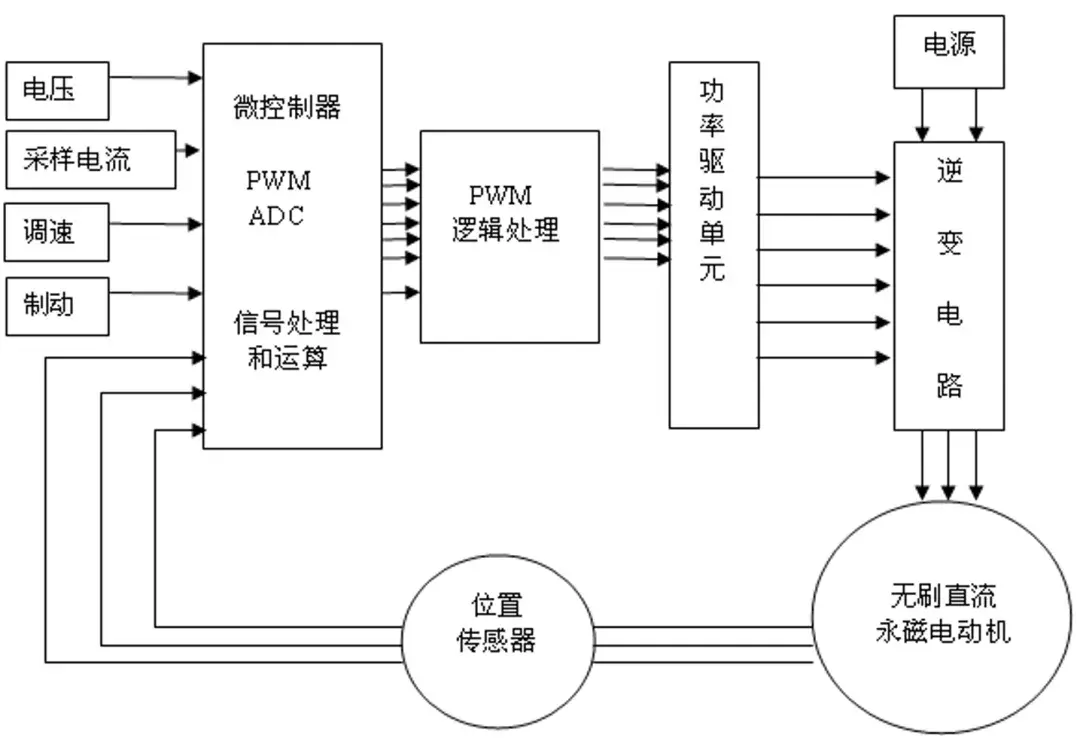

在无刷直流(BLDC)电机的控制系统中,6路PWM信号精准控制上下桥MOSFET的开关是核心。你是否注意到,驱动IC对PWM高低电平有效性的配置,经历了从“上高下低”到“上高下高”的显著转变?这背后不仅仅是逻辑定义的不同,更是技术与可靠性的进化。今天,我们就来揭秘这两种PWM配置逻辑的本质与选择依据。

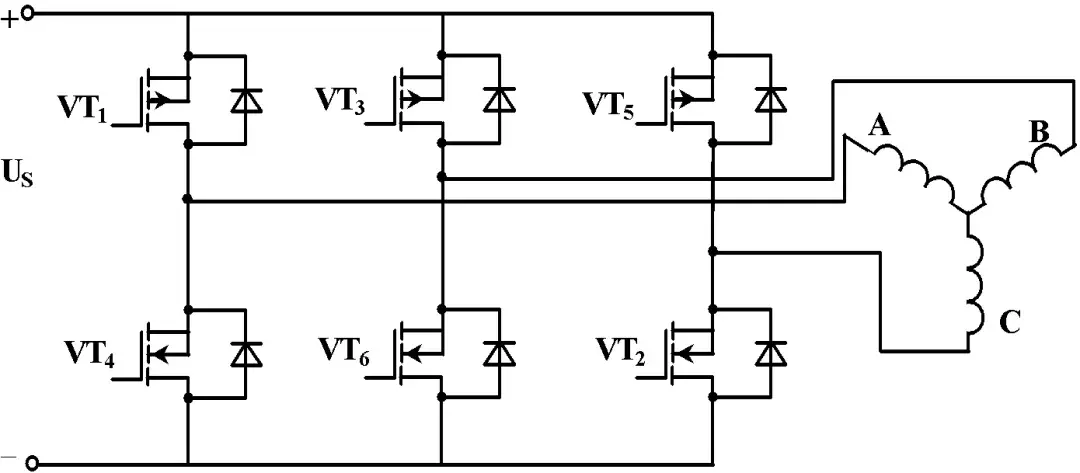

图:三相BLDC换相电路示意

一、PWM控制基础:理解“有效电平”

驱动IC的核心任务之一,是将来自MCU的低功率PWM信号“翻译”成足以驱动MOSFET栅极的强信号。关键点在于,它需要明确定义PWM信号何种电平代表开启对应的MOSFET。

1.“上高下高” (Active High for Both):

定义: 无论是上桥臂还是下桥臂MOSFET,其对应的PWM输入高电平代表开启指令;低电平代表关闭指令。

示意: 上桥PWM: 高电平 -> 上MOS管ON 下桥PWM: 高电平 -> 下MOS管ON 两者低电平 -> 对应MOS管OFF

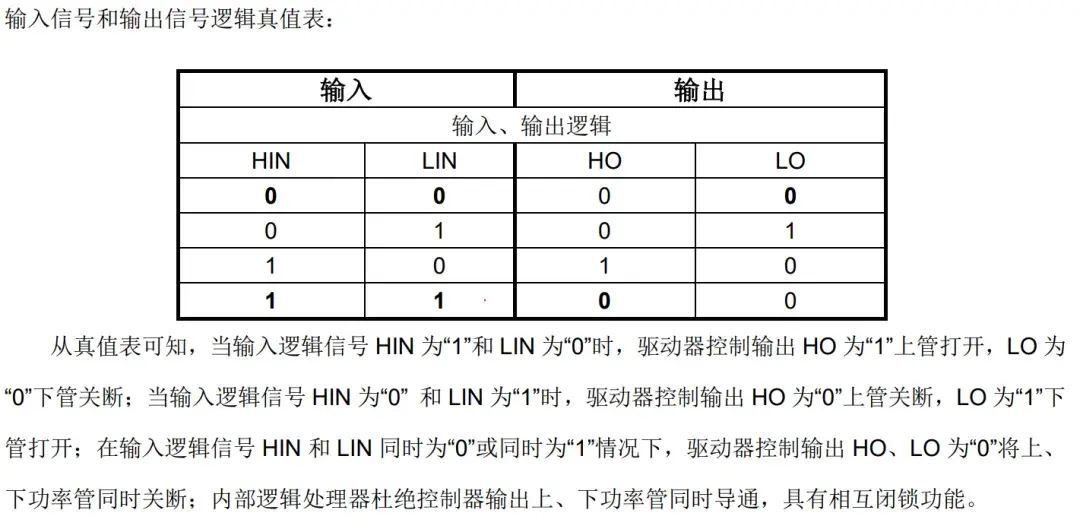

核心要求: 绝不允许 同一相的上下桥PWM 同时为高电平,否则会造成可怕的直通短路(Shoot-Through),瞬间烧毁MOSFET!

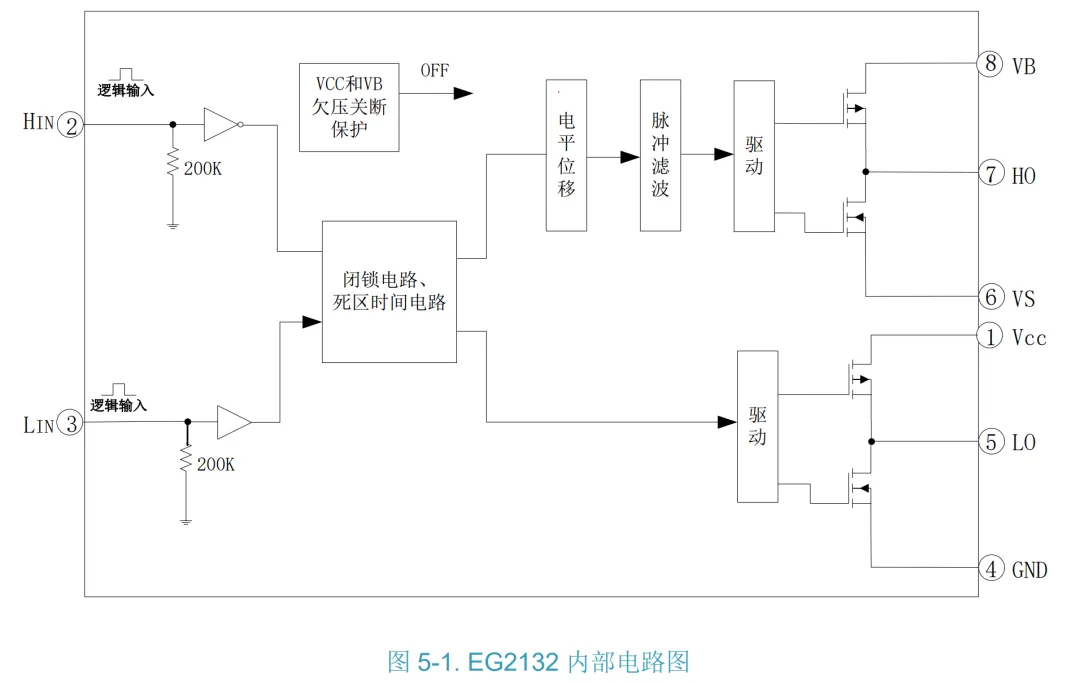

图:以屹晶微的EG2132为例,是典型的上高下高控制

2.“上高下低” (Active High for Top, Active Low for Bottom):

定义: 上桥臂MOSFET对应的PWM输入,高电平代表开启;下桥臂MOSFET对应的PWM输入,低电平代表开启(相当于“有效低”)。

示意: 上桥PWM: 高电平 -> 上MOS管ON 下桥PWM:低电平-> 下MOS管ON (注意这里是低电平有效!) 上桥低电平且下桥高电平 -> 对应MOS管OFF

核心要求: 绝不允许 同一相的PWM出现 上桥为高、下桥为低 的组合,这也是导致直通短路的致命组合!

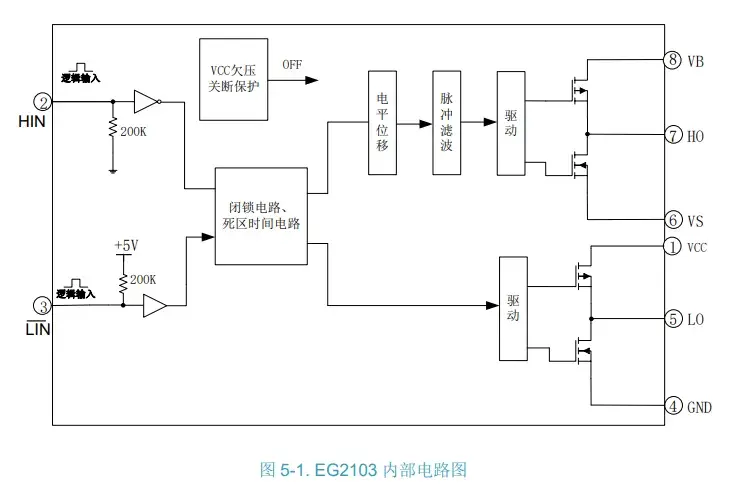

图:以屹晶微的EG2103为例,是典型的上高下低控制

二、永恒不变的铁律:严防死守“直通”

无论采用哪种逻辑配置,防止同一相的上下桥MOSFET同时导通是设计驱动的核心死命令。这是所有驱动IC设计中优先级最高的任务。现代驱动IC通常具备以下关键保护机制:

集成死区时间控制 (Integrated Dead Time): 确保在上下桥切换的瞬间,预留一段两者都关闭的安全时间,彻底杜绝因开关延迟导致的瞬态直通。

高级防护电路: 针对可能引起意外导通的现象(如MOSFET关断时栅极的电压振铃Ring、栅极承受过大的负压dv/dt等),内置防护电路,大幅提升系统鲁棒性。

图:以屹晶微的EG2132的真值表为例

三、历史的烙印:为何曾是“上高下低”的天下?

回顾早期BLDC驱动方案,驱动IC的集成度、工艺水平和内部逻辑复杂度有限。想要在外部可靠地实现防止上高下低(即上桥高+下桥低)同时出现的直通组合,硬件逻辑上有一个“巧妙”的解决方案:使用简单的与非门电路(NAND gate)。

图:约20年前的无刷电机控制系统框图,可见其复杂

“上高下低”的硬件优势: 对于下桥臂“低电平有效”的设计,将下桥的PWM输入信号取反后再控制MOSFET,其逻辑恰好可以通过一个简单的与非门实现。这种方案在当时硬件资源受限的情况下,成本低、实现相对简单、可靠性满足基本要求,因此“上高下低”逻辑成为了早期驱动设计的主流选择。

四、时代的进步:为何现在主流是“上高下高”?

技术的洪流滚滚向前。现代栅极驱动IC的制造工艺、集成能力和设计复杂度已经今非昔比。内部的数字逻辑、高精度死区控制、先进保护功能都高度集成化。在这种背景下,“上高下高”逻辑的优势被充分发挥,逐渐成为新设计的首选:

更高的抗干扰能力: “上高下低”要求MCU对下桥PWM输出低电平作为有效开启信号。在复杂的电磁环境中,低电平信号更容易受到干扰,误触发MOSFET开启的风险略高。而“上高下高”的开启都是高电平,干扰使其达到有效门槛的可能性相对较低。

更符合直觉的逻辑: “高电平开启”对于大多数工程师来说,是更自然、更符合直觉的逻辑定义方式(比如继电器的控制、普通GPIO点亮LED等)。设计理解和代码编写更容易,降低人为错误的可能性。“上高下低”的混合逻辑(上桥高有效,下桥低有效)则需要额外的思维转换,增加认知负担。

上下电状态更可靠: MCU在启动或复位时,IO口往往处于默认的低电平或高阻态。“上高下高”逻辑下,这种默认状态会自然地关闭所有MOSFET,带来更高的上电安全性。而对于“上高下低”逻辑,MCU的下桥口在默认输出低电平(或某些配置下的状态)时,可能就对应于下桥MOSFET的意外开启状态,存在一定风险。

简化接口设计: 随着驱动IC集成度提高,复杂的防直通逻辑都放在了IC内部,不需要再依赖外部的逻辑门电路。工程师只需关注“输出高代表开启”这一统一指令即可,接口设计更简洁。

五、总结:可靠性至上的选择

驱动IC中PWM逻辑从“上高下低”到“上高下高”的演变,清晰地展现了技术升级的路径:从早期依赖外部逻辑应对资源限制的“权宜之计”,发展到依托高度集成化IC实现内在逻辑优化和可靠性提升的“最优解”。现代“上高下高”配置凭借其优异的抗干扰性能、符合直觉的接口、更高的上下电安全性,以及对驱动IC先进内建保护机制的完美契合,成为了当今高性能、高可靠性BLDC控制系统设计的首选逻辑方案。工程师小贴士: 在选用驱动IC设计新系统时,务必查阅数据手册,明确其上下桥输入的有效电平定义!多数现代芯片已默认采用“上高下高”逻辑。了解这一趋势,有助于你做出更符合时代、更可靠的系统设计决策。

审核编辑 黄宇

-

IC

+关注

关注

36文章

6140浏览量

180101 -

BLDC

+关注

关注

213文章

838浏览量

98512 -

无刷电机

+关注

关注

60文章

905浏览量

47636

发布评论请先 登录

BLDC驱动必修课:为何现代MOSFET驱动IC偏爱“上高下高”逻辑???

星火杯--西电学子的必修课

Cadence高速PCB设计电子布局工程师必修课程视频教程

用于BLDC电机驱动的MOSFET选择

三相BLDC电机驱动器混合IC

电源工程师必修知识:PFC调试视频及原理图资料

驱动BLDC电机的半桥开启高端和低端MOSFET

购买品牌笔记本必修课程

功率 MOSFET 在汽车 BLDC 和 PMSM 驱动器中的应用-AN50009

BLDC驱动必修课:为何现代MOSFET驱动IC偏爱“上高下高”逻辑?

BLDC驱动必修课:为何现代MOSFET驱动IC偏爱“上高下高”逻辑?

评论